# +30 V/±15 V Operation 128-Position Digital Potentiometer

AD7376

o

D

7-BIT SERIAL

REGISTER

GND

ск

7

SDC

SDI

CLK CS FUNCTIONAL BLOCK DIAGRAM

7-BIT LATCH

R

RS

Figure 1.

# AD7376

Υνσ

B

Vss

SHDN

SHDN

### **FEATURES**

128 positions 10 kΩ, 50 kΩ, 100 kΩ 5 V to 30 V single-supply operation ±5 V to ±15 V dual-supply operation 3-wire SPI®-compatible serial interface THD 0.006% typical Programmable preset Power shutdown: less than 1 μA *i*CMOS<sup>™</sup> process technology

### **APPLICATIONS**

High voltage DAC Programmable power supply Programmable gain and offset adjustment Programmable filters, delays Actuator control Audio volume control Mechanical potentiometer replacement

### **GENERAL DESCRIPTION**

The AD7376<sup>1</sup> is one of the few high voltage, high performance digital potentiometers<sup>2</sup> on the market. This device can be used as a programmable resistor or resistor divider. The AD7376 performs the same electronic adjustment function as mechanical potentiometers, variable resistors, and trimmers with enhanced resolution, solid-state reliability, and programmability. With digital rather than manual control, the AD7376 provides layout flexibility and allows closed-loop dynamic controllability.

The AD7376 features sleep-mode programmability in shutdown that can be used to program the preset before device activation, thus providing an alternative to costly EEPROM solutions.

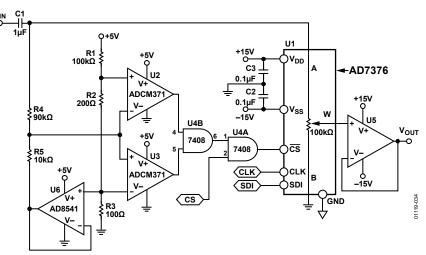

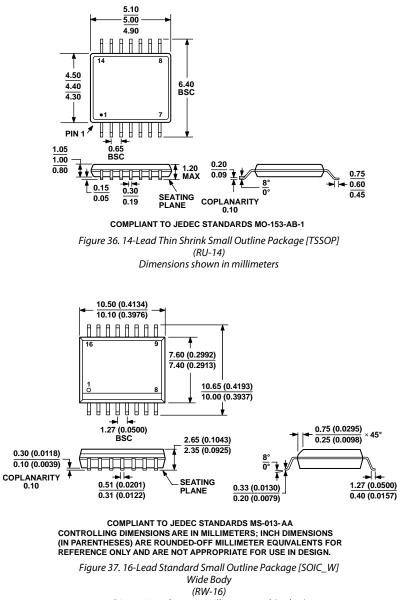

The AD7376 is available in 14-lead TSSOP and 16-lead wide body SOIC packages in 10 k $\Omega$ , 50 k $\Omega$ , and 100 k $\Omega$  options. All parts are guaranteed to operate over the -40°C to +85°C extended industrial temperature range.

<sup>1</sup>Patent number: 54952455.

<sup>2</sup> The terms *digital potentiometer* and *RDAC* are used interchangeably.

#### Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features                                                           |

|--------------------------------------------------------------------|

| Applications1                                                      |

| Functional Block Diagram 1                                         |

| General Description                                                |

| Revision History                                                   |

| Specifications                                                     |

| Electrical Characteristics—10 kΩ Version                           |

| Electrical Characteristics—50 k $\Omega$ , 100 k $\Omega$ Versions |

| Timing Specifications                                              |

| 3-Wire Digital Interface                                           |

| Absolute Maximum Ratings7                                          |

| ESD Caution7                                                       |

| Pin Configurations and Function Descriptions                       |

| Typical Performance Characteristics                                |

| Theory of Operation                                                |

### **REVISION HISTORY**

| 3/07—Rev. A to Rev. B                                       |        |

|-------------------------------------------------------------|--------|

| Updated FormatUniv                                          | versal |

| Changes to Absolute Maximum Ratings                         | 7      |

| Changes to ESD Protection Section                           |        |

| Changes to Ordering Guide                                   |        |

| 11/05—Rev. 0 to Rev. A                                      |        |

| Updated FormatUniv                                          | versal |

| Deleted DIP PackageUniv                                     | versal |

| Changes to Features                                         | 1      |

| Separated Electrical Characteristics into Table 1 and Table | 2 3    |

| Separated Interface Timing into Table 3                     | 5      |

| Changes to Table 1 Through Table 3                          | 3      |

| Added Table 4                                               | 6      |

| Added Figure 2                                              | 6      |

| Changes to Absolute Maximum Ratings Section                 | 7      |

| Deleted Parametric Test Circuits Section                    | 7      |

| Changes to Typical Performance Characteristics              | 9      |

| Added Daisy-Chain Operation Section                         | 14     |

| Added ESD Protection Section                                | 14     |

| Added Terminal Voltage Operating Range Section              | 14     |

| Added Power-Up and Power-Down Sequences Section             | 14     |

| Added Layout and Power Supply Biasing Section               | 15     |

| Added Applications Section                                  | 16     |

| Updated Outline Dimensions                                  | 18     |

| Changes to Ordering Guide                                   | 19     |

|                                                             |        |

10/97—Revision 0: Initial Version

|   | Programming the Variable Resistor     | 12 |

|---|---------------------------------------|----|

|   | Programming the Potentiometer Divider | 13 |

|   | 3-Wire Serial Bus Digital Interface   | 13 |

|   | Daisy-Chain Operation                 | 14 |

|   | ESD Protection                        | 14 |

|   | Terminal Voltage Operating Range      | 14 |

|   | Power-Up and Power-Down Sequences     | 14 |

|   | Layout and Power Supply Biasing       | 15 |

| A | pplications Information               | 16 |

|   | High Voltage DAC                      | 16 |

|   | Programmable Power Supply             | 16 |

|   | Audio Volume Control                  | 17 |

| 0 | utline Dimensions                     | 18 |

|   | Ordering Guide                        | 19 |

|   |                                       |    |

## **SPECIFICATIONS**

### ELECTRICAL CHARACTERISTICS—10 k $\Omega$ VERSION

$V_{\text{DD}}/V_{\text{SS}} = \pm 15 \text{ V} \pm 10\%, V_{\text{A}} = V_{\text{DD}}, V_{\text{B}} = V_{\text{SS}}/0 \text{ V}, -40^{\circ}\text{C} < T_{\text{A}} < +85^{\circ}\text{C}, \text{ unless otherwise noted.}$

| Parameter                                         | Symbol                                       | Conditions                                                                               | Min  | Typ <sup>1</sup> | Max             | Unit   |

|---------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------|------|------------------|-----------------|--------|

| DC CHARACTERISTICS—                               |                                              |                                                                                          |      |                  |                 |        |

| RHEOSTAT MODE                                     |                                              |                                                                                          |      |                  |                 |        |

| Resistor Differential Nonlinearity <sup>2</sup>   | R-DNL                                        | $R_{WB}$ , $V_A = NC$ , $V_{DD}/V_{SS} = \pm 15 V$                                       | -1   | ±0.5             | +1              | LSB    |

| Resistor Nonlinearity <sup>2</sup>                | R-INL                                        | $R_{WB}, V_A = NC, V_{DD}/V_{SS} = \pm 15 V$                                             | -1   | ±0.5             | +1              | LSB    |

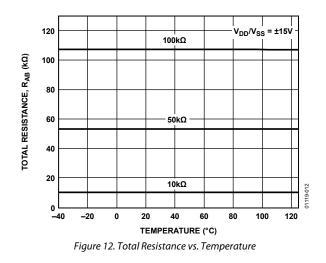

| Nominal Resistor Tolerance                        | $\Delta R_{AB}$                              | $T_A = 25^{\circ}C$                                                                      | -30  |                  | +30             | %      |

| Resistance Temperature Coefficient <sup>3</sup>   | $(\Delta R_{AB}/R_{AB})/\Delta T 	imes 10^6$ | $V_{AB} = V_{DD}$ , wiper = no connect                                                   |      | -300             |                 | ppm/°C |

| Wiper Resistance                                  | Rw                                           | $V_{DD}/V_{SS} = \pm 15 V$                                                               |      | 120              | 200             | Ω      |

|                                                   |                                              | $V_{DD}/V_{SS} = \pm 5 V$                                                                |      | 260              |                 | Ω      |

| DC CHARACTERISTICS—<br>POTENTIOMETER DIVIDER MODE |                                              |                                                                                          |      |                  |                 |        |

| Integral Nonlinearity <sup>4</sup>                | INL                                          | $V_{DD}/V_{SS} = \pm 15 V$                                                               | -1   | ±0.5             | +1              | LSB    |

| Differential Nonlinearity <sup>4</sup>            | DNL                                          | $V_{DD}/V_{SS} = \pm 15 V$                                                               | -1   | ±0.5             | +1              | LSB    |

| Voltage Divider Temperature<br>Coefficient        | $(\Delta V_W/V_W)/\Delta T \times 10^6$      | Code = 0x40                                                                              |      | 5                |                 | ppm/°C |

| Full-Scale Error                                  | V <sub>WFSE</sub>                            | $Code = 0x7F, V_{DD}/V_{SS} = \pm 15 V$                                                  | -3   | -1.5             | 0               | LSB    |

| Zero-Scale Error                                  | V <sub>WZSE</sub>                            | $Code = 0x00, V_{DD}/V_{SS} = \pm 15 V$                                                  | 0    | 1.5              | 3               | LSB    |

| RESISTOR TERMINALS                                |                                              |                                                                                          |      |                  |                 |        |

| Voltage Range⁵                                    | <b>V</b> A, B, W                             |                                                                                          | Vss  |                  | $V_{\text{DD}}$ | V      |

| Capacitance <sup>6</sup> A, B                     | Са, в                                        | f = 1 MHz, measured to GND,<br>code = 0x40                                               |      | 45               |                 | pF     |

| Capacitance <sup>6</sup>                          | Cw                                           | f = 1 MHz, measured to GND,<br>code = 0x40                                               |      | 60               |                 | pF     |

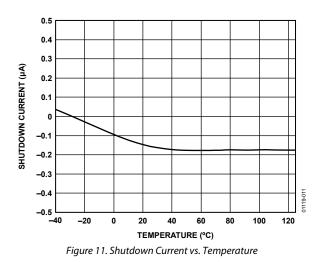

| Shutdown Supply Current <sup>7</sup>              | I <sub>A_SD</sub>                            | $V_A = V_{DD}, V_B = 0 V, \overline{SHDN} = 0$                                           |      | 0.02             | 1               | μA     |

| Shutdown Wiper Resistance                         | Rw_sd                                        | $V_A = V_{DD}$ , $V_B = 0 V$ , $\overline{SHDN} = 0$ , $V_{DD} = 15 V$                   |      | 170              | 400             | Ω      |

| Common-Mode Leakage                               | Ісм                                          | $V_A = V_B = V_W$                                                                        |      | 1                |                 | nA     |

| DIGITAL INPUTS AND OUTPUTS                        |                                              |                                                                                          |      |                  |                 |        |

| Input Logic High                                  | VIH                                          | $V_{DD} = 5 V \text{ or } 15 V$                                                          | 2.4  |                  |                 | v      |

| Input Logic Low                                   | VIL                                          | $V_{DD} = 5 V \text{ or } 15 V$                                                          |      |                  | 0.8             | V      |

| Output Logic High                                 | V <sub>OH</sub>                              | $R_{Pull-Up} = 2.2 \text{ k}\Omega \text{ to 5 V}$                                       | 4.9  |                  |                 | V      |

| Output Logic Low                                  | Vol                                          | $I_{OL} = 1.6 \text{ mA}, V_{LOGIC} = 5 \text{ V}, V_{DD} = 15 \text{ V}$                |      |                  | 0.4             | V      |

| Input Current                                     | IIL                                          | $V_{IN} = 0 V \text{ or } 5 V$                                                           |      |                  | ±1              | μA     |

| Input Capacitance <sup>6</sup>                    | CIL                                          |                                                                                          |      | 5                |                 | pF     |

| POWER SUPPLIES                                    |                                              |                                                                                          |      |                  |                 |        |

| Power Supply Range                                | V <sub>DD</sub> /V <sub>SS</sub>             | Dual-supply range                                                                        | ±4.5 |                  | ±16.5           | V      |

| Power Supply Range                                | V <sub>DD</sub>                              | Single-supply range, $V_{SS} = 0$                                                        | 4.5  |                  | 33              | V      |

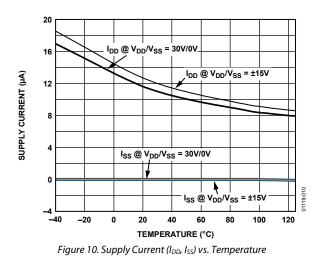

| Positive Supply Current                           | IDD                                          | $V_{IH} = 5 V \text{ or } V_{IL} = 0 V, V_{DD}/V_{SS} = \pm 15 V$                        |      |                  | 2               | mA     |

|                                                   |                                              | $V_{IH} = 5 \text{ V or } V_{IL} = 0 \text{ V}, V_{DD}/V_{SS} = \pm 5 \text{ V}$         |      | 12               | 25              | μA     |

| Negative Supply Current                           | lss                                          | $V_{IH} = 5 \text{ V or } V_{IL} = 0 \text{ V}, V_{DD}/V_{SS} = \pm 15 \text{ V}$        |      |                  | -0.1            | mA     |

|                                                   |                                              | $V_{IH} = 5 \text{ V} \text{ or } V_{IL} = 0 \text{ V}, V_{DD}/V_{SS} = \pm 5 \text{ V}$ |      |                  | -0.1            | mA     |

| Power Dissipation <sup>8</sup>                    | P <sub>DISS</sub>                            | $V_{IH}=5~V~or~V_{IL}=0~V, V_{DD}/V_{SS}=\pm15~V$                                        |      |                  | 31.5            | mW     |

| Power Supply Rejection Ratio                      | PSRR                                         | $\Delta V_{DD}/\Delta V_{SS} = \pm 15 \text{ V} \pm 10\%$                                | -0.2 | ±0.05            | +0.2            | %/%    |

| Parameter                                   | Symbol | Conditions                                          | Min | <b>Typ</b> <sup>1</sup> | Мах | Unit  |

|---------------------------------------------|--------|-----------------------------------------------------|-----|-------------------------|-----|-------|

| DYNAMIC CHARACTERISTICS <sup>6, 9, 10</sup> |        |                                                     |     |                         |     |       |

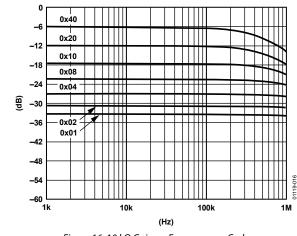

| Bandwidth –3 dB                             | BW     | Code = 0x40                                         |     | 470                     |     | kHz   |

| Total Harmonic Distortion                   | THDw   | $V_A = 1 V rms$ , $V_B = 0 V$ , $f = 1 kHz$         |     | 0.006                   |     | %     |

| V <sub>w</sub> Settling Time                | ts     | $V_A = 10 V$ , $V_B = 0 V$ , $\pm 1 LSB$ error band |     | 4                       |     | μs    |

| Resistor Noise Voltage                      | ел_wв  | $R_{WB} = 5 k\Omega, f = 1 kHz$                     |     | 0.9                     |     | nV√Hz |

<sup>1</sup> Typical values represent average readings at 25°C,  $V_{DD} = 15$  V, and  $V_{SS} = -15$  V.

<sup>2</sup> Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum and minimum resistance wiper positions. R-DNL measures the relative step change from an ideal value measured between successive tap positions. Parts are guaranteed monotonic.

<sup>3</sup> Pb-free parts have a 35 ppm/°C temperature coefficient (tempco).

<sup>4</sup> INL and DNL are measured at V<sub>w</sub> with the RDAC configured as a potentiometer divider, similar to a voltage output digital-to-analog converter.  $V_A = V_{DD}$  and  $V_B = 0$  V. DNL specification limits of  $\pm 1$  LSB maximum are guaranteed monotonic operating conditions.

<sup>5</sup> Resistor Terminals A, B, and W have no limitations on polarity with respect to each other.

<sup>6</sup> Guaranteed by design and not subject to production test.

<sup>7</sup> Measured at the A terminal. A terminal is open circuit in shutdown mode.

<sup>8</sup> P<sub>DISS</sub> is calculated from  $(I_{DD} \times V_{DD})$  + abs $(I_{SS} \times V_{SS})$ . CMOS logic level inputs result in minimum power dissipation.

<sup>9</sup> Bandwidth, noise, and settling times are dependent on the terminal resistance value chosen. The lowest R value results in the fastest settling time and highest bandwidth. The highest R value results in the minimum overall power consumption.  $^{10}$  All dynamic characteristics use  $V_{\text{DD}}$  = 15 V and  $V_{\text{SS}}$  = –15 V.

### **ELECTRICAL CHARACTERISTICS—50 kΩ, 100 kΩ VERSIONS**

$V_{DD}/V_{SS} = \pm 15 \text{ V} \pm 10\% \text{ or } \pm 5 \text{ V} \pm 10\%, V_A = V_{DD}, V_B = V_{SS}/0 \text{ V}, -40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}$ , unless otherwise noted.

| Parameter                                         | Symbol                                          | Conditions                                                             | Min  | Typ <sup>1</sup> | Max             | Unit   |

|---------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------|------|------------------|-----------------|--------|

| DC CHARACTERISTICS—RHEOSTAT MODE                  | -                                               |                                                                        |      |                  |                 |        |

| Resistor Differential Nonlinearity <sup>2</sup>   | R-DNL                                           | $R_{WB}$ , $V_A = NC$                                                  | -1   | ±0.5             | +1              | LSB    |

| Resistor Nonlinearity <sup>2</sup>                | R-INL                                           | $R_{WB}$ , $V_A = NC$ , $R_{AB} = 50 \text{ k}\Omega$                  | -1.5 | ±0.5             | +1.5            | LSB    |

|                                                   |                                                 | $R_{WB}$ , $V_A = NC$ , $R_{AB} = 100 \text{ k}\Omega$                 | -1   | ±0.5             | +1              | LSB    |

| Nominal Resistor Tolerance                        | $\Delta R_{AB}$                                 | $T_A = 25^{\circ}C$                                                    | -30  |                  | +30             | %      |

| Resistance Temperature Coefficient <sup>3</sup>   | $(\Delta R_{AB}/R_{AB})/\Delta T \times 10^{6}$ | $V_{AB} = V_{DD}$ , wiper = no connect                                 |      | -300             |                 | ppm/°C |

| Wiper Resistance                                  | Rw                                              | $V_{DD}/V_{SS} = \pm 15 V$                                             |      | 120              | 200             | Ω      |

|                                                   |                                                 | $V_{DD}/V_{SS} = \pm 5 V$                                              |      | 260              |                 | Ω      |

| DC CHARACTERISTICS—<br>POTENTIOMETER DIVIDER MODE |                                                 |                                                                        |      |                  |                 |        |

| Integral Nonlinearity <sup>4</sup>                | INL                                             |                                                                        | -1   | ±0.5             | +1              | LSB    |

| Differential Nonlinearity <sup>4</sup>            | DNL                                             |                                                                        | -1   | ±0.5             | +1              | LSB    |

| Voltage Divider Temperature<br>Coefficient        | $(\Delta V_W/V_W)/\Delta T 	imes 10^6$          | Code = 0x40                                                            |      | 5                |                 | ppm/°C |

| Full-Scale Error                                  | V <sub>WFSE</sub>                               | Code = 0x7F                                                            | -2   | -0.5             | 0               | LSB    |

| Zero-Scale Error                                  | V <sub>wzse</sub>                               | Code = 0x00                                                            | 0    | 0.5              | 1               | LSB    |

| RESISTOR TERMINALS                                |                                                 |                                                                        |      |                  |                 |        |

| Voltage Range⁵                                    | <b>V</b> A, B, W                                |                                                                        | Vss  |                  | $V_{\text{DD}}$ | V      |

| Capacitance <sup>6</sup> A, B                     | С <sub>А, В</sub>                               | f = 1 MHz, measured to GND,<br>code = 0x40                             |      | 45               |                 | pF     |

| Capacitance <sup>6</sup> C <sub>w</sub>           |                                                 | f = 1 MHz, measured to GND,<br>code = 0x40                             |      | 60               |                 | pF     |

| Shutdown Supply Current <sup>7</sup>              | I <sub>A_SD</sub>                               | $V_A = V_{DD}, V_B = 0 V, \overline{SHDN} = 0$                         |      | 0.02             | 1               | μΑ     |

| Shutdown Wiper Resistance                         | Rw_sd                                           | $V_A = V_{DD}$ , $V_B = 0 V$ , $\overline{SHDN} = 0$ , $V_{DD} = 15 V$ |      | 170              | 400             | Ω      |

| Common-Mode Leakage                               | ICM                                             | $V_A = V_B = V_W$                                                      |      | 1                |                 | nA     |

| Parameter                                   | Symbol                           | Conditions                                                                | Min   | Typ <sup>1</sup> | Max   | Unit  |

|---------------------------------------------|----------------------------------|---------------------------------------------------------------------------|-------|------------------|-------|-------|

| DIGITAL INPUTS AND OUTPUTS                  |                                  |                                                                           |       |                  |       |       |

| Input Logic High                            | VIH                              | $V_{DD} = 5 V \text{ or } 15 V$                                           | 2.4   |                  |       | V     |

| Input Logic Low                             | VIL                              | $V_{DD} = 5 V \text{ or } 15 V$                                           |       |                  | 0.8   | V     |

| Output Logic High                           | V <sub>он</sub>                  | $R_{Pull-Up} = 2.2 \text{ k}\Omega \text{ to } 5 \text{ V}$               | 4.9   |                  |       | V     |

| Output Logic Low                            | Vol                              | $I_{OL} = 1.6 \text{ mA}, V_{LOGIC} = 5 \text{ V}, V_{DD} = 15 \text{ V}$ |       |                  | 0.4   | V     |

| Input Current                               | lı.                              | $V_{IN} = 0 V \text{ or } 5 V$                                            |       |                  | ±1    | μA    |

| Input Capacitance <sup>6</sup>              | CIL                              |                                                                           |       | 5                |       | pF    |

| POWER SUPPLIES                              |                                  |                                                                           |       |                  |       |       |

| Power Supply Range                          | V <sub>DD</sub> /V <sub>SS</sub> | Dual-supply range                                                         | ±4.5  |                  | ±16.5 | V     |

| Power Supply Range                          | V <sub>DD</sub>                  | Single-supply range, $V_{ss} = 0$                                         | 4.5   |                  | 33    | V     |

| Positive Supply Current                     | IDD                              | $V_{IH} = 5 V \text{ or } V_{IL} = 0 V, V_{DD}/V_{SS} = \pm 15 V$         |       |                  | 2     | mA    |

|                                             |                                  | $V_{IH} = 5$ V or $V_{IL} = 0$ V, $V_{DD}/V_{SS} = \pm 5$ V               |       | 12               | 25    | μΑ    |

| Negative Supply Current                     | lss                              | $V_{IH} = 5$ V or $V_{IL} = 0$ V, $V_{DD}/V_{SS} = \pm 15$ V              |       |                  | -0.1  | mA    |

|                                             |                                  | $V_{IH} = 5$ V or $V_{IL} = 0$ V, $V_{DD}/V_{SS} = \pm 5$ V               |       |                  | -0.1  | mA    |

| Power Dissipation <sup>8</sup>              | P <sub>DISS</sub>                | $V_{IH} = 5 V \text{ or } V_{IL} = 0 V, V_{DD}/V_{SS} = \pm 15 V$         |       |                  | 31.5  | mW    |

| Power Supply Rejection Ratio                | PSRR                             |                                                                           | -0.25 | ±0.1             | +0.25 | %/%   |

| DYNAMIC CHARACTERISTICS <sup>6, 9, 10</sup> |                                  |                                                                           |       |                  |       |       |

| Bandwidth –3 dB                             | BW                               | $R_{AB} = 50 \text{ k}\Omega$ , code = 0x40                               |       | 90               |       | kHz   |

|                                             |                                  | $R_{AB} = 100 \text{ k}\Omega$ , code = 0x40                              |       | 50               |       | kHz   |

| Total Harmonic Distortion                   | THDw                             | $V_A = 1 V rms$ , $V_B = 0 V$ , $f = 1 kHz$                               |       | 0.002            |       | %     |

| V <sub>w</sub> Settling Time                | ts                               | $V_A = 10 V$ , $V_B = 0 V$ , $\pm 1 LSB$ error band                       |       | 4                |       | μs    |

| Resistor Noise Voltage                      | e <sub>N_WB</sub>                | $R_{WB} = 25 \text{ k}\Omega, f = 1 \text{ kHz}$                          |       | 2                |       | nV√Hz |

$^{1}$  Typical values represent average readings at 25°C,  $V_{\text{DD}}$  = 15 V, and  $V_{\text{SS}}$  = –15 V.

<sup>2</sup> Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum and minimum resistance wiper positions. R-DNL measures the relative step change from an ideal value measured between successive tap positions. Parts are guaranteed monotonic.

<sup>3</sup> Pb-free parts have a 35 ppm/°C temperature coefficient. <sup>4</sup> INL and DNL are measured at V<sub>W</sub> with the RDAC configured as a potentiometer divider, similar to a voltage output digital-to-analog converter.  $V_A = V_{DD}$  and  $V_B = 0$  V. DNL specification limits of ±1 LSB maximum are guaranteed monotonic operating conditions.

<sup>5</sup> Resistor Terminals A, B, and W have no limitations on polarity with respect to each other.

<sup>6</sup> Guaranteed by design and not subject to production test.

<sup>7</sup> Measured at the A terminal. A terminal is open circuit in shutdown mode.

$^{8}$  P<sub>DISS</sub> is calculated from (I<sub>DD</sub> × V<sub>DD</sub>) + abs(I<sub>SS</sub> × V<sub>SS</sub>). CMOS logic level inputs result in minimum power dissipation.

<sup>9</sup> Bandwidth, noise, and settling times are dependent on the terminal resistance value chosen. The lowest R value results in the fastest settling time and highest

bandwidth. The highest R value results in the minimum overall power consumption.

<sup>10</sup> All dynamic characteristics use  $V_{DD} = 15$  V and  $V_{SS} = -15$  V.

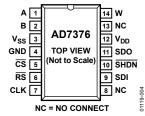

### **TIMING SPECIFICATIONS**

#### Table 3.

| Parameter                                        | Symbol                            | Conditions                                               | Min | Тур | Max | Unit |

|--------------------------------------------------|-----------------------------------|----------------------------------------------------------|-----|-----|-----|------|

| INTERFACE TIMING CHARACTERISTICS <sup>1, 2</sup> |                                   |                                                          |     |     |     |      |

| Clock Frequency                                  | fclk                              |                                                          |     |     | 4   | MHz  |

| Input Clock Pulse Width                          | t <sub>cн</sub> , t <sub>cl</sub> | Clock level high or low                                  | 120 |     |     | ns   |

| Data Setup Time                                  | t <sub>DS</sub>                   |                                                          | 30  |     |     | ns   |

| Data Hold Time                                   | t <sub>DH</sub>                   |                                                          | 20  |     |     | ns   |

| CLK to SDO Propagation Delay <sup>3</sup>        | t <sub>PD</sub>                   | $R_{Pull-Up} = 2.2 \text{ k}\Omega, C_L < 20 \text{ pF}$ | 10  |     | 100 | ns   |

| CS Setup Time                                    | t <sub>css</sub>                  |                                                          | 120 |     |     | ns   |

| CS High Pulse Width                              | tcsw                              |                                                          | 150 |     |     | ns   |

| Reset Pulse Width                                | t <sub>RS</sub>                   |                                                          | 120 |     |     | ns   |

| CLK Fall to CS Fall Hold Time                    | t <sub>CSH0</sub>                 |                                                          | 10  |     |     | ns   |

| CLK Rise to CS Rise Hold Time                    | t <sub>CSH</sub>                  |                                                          | 120 |     |     | ns   |

| CS Rise to Clock Rise Setup                      | t <sub>CS1</sub>                  |                                                          | 120 |     |     | ns   |

<sup>1</sup> Guaranteed by design and not subject to production test.

<sup>2</sup> See Figure 3 for the location of the measured values. All input control voltages are specified with  $t_R = t_F = 1$  ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of 1.6 V.

Switching characteristics are measured using  $V_{DD} = 15$  V and  $V_{SS} = -15$  V.

$^3$  Propagation delay depends on value of  $V_{\text{DD}}, \overline{R_{\text{Pull-Up}}}, \text{and } C_L.$

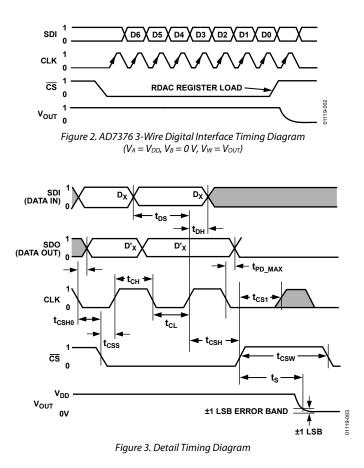

## **3-WIRE DIGITAL INTERFACE**

### Table 4. AD7376 Serial Data-Word Format<sup>1</sup>

| MSB            |    |    |    |    |    | LSB            |

|----------------|----|----|----|----|----|----------------|

| D6             | D5 | D4 | D3 | D2 | D1 | D0             |

| 2 <sup>6</sup> |    |    |    |    |    | 2 <sup>0</sup> |

<sup>1</sup> Data is loaded MSB first.

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

### Table 5.

| Parameter                                                                                           | Rating                           |

|-----------------------------------------------------------------------------------------------------|----------------------------------|

| V <sub>DD</sub> to GND                                                                              | –0.3 V to +35 V                  |

| Vss to GND                                                                                          | +0.3 V to -16.5 V                |

| V <sub>DD</sub> to V <sub>SS</sub>                                                                  | –0.3 V to +35 V                  |

| V <sub>A</sub> , V <sub>B</sub> , V <sub>W</sub> to GND                                             | Vss to VDD                       |

| Maximum Current                                                                                     |                                  |

| I <sub>WB</sub> , I <sub>WA</sub> Pulsed                                                            | ±20 mA                           |

| $I_{WB}$ Continuous ( $R_{WB} \le 6 k\Omega$ , A open,<br>$V_{DD}/V_{SS} = 30 V/0 V$ ) <sup>1</sup> | ±5 mA                            |

| $I_{WA}$ Continuous ( $R_{WA} \le 6 k\Omega$ , B open,<br>$V_{DD}/V_{SS} = 30 V/0 V$ ) <sup>1</sup> | ±5 mA                            |

| Digital Input and Output Voltages to GND                                                            | 0 V to V <sub>DD</sub> + $0.3$ V |

| Operating Temperature Range                                                                         | -40°C to +85°C                   |

| Maximum Junction Temperature $(T_{JMAX})^2$                                                         | 150°C                            |

| Storage Temperature Range                                                                           | –65°C to +150°C                  |

| Reflow Soldering                                                                                    |                                  |

| Peak Temperature                                                                                    | 260°C                            |

| Time at Peak Temperature                                                                            | 20 sec to 40 sec                 |

| Package Power Dissipation                                                                           | $(T_{JMAX} - T_A)/\Theta_{JA}$   |

| Thermal Resistance $\theta_{JA}$                                                                    |                                  |

| 16-Lead SOIC_W                                                                                      | 120°C/W                          |

| 14-Lead TSSOP                                                                                       | 240°C/W                          |

<sup>1</sup> Maximum terminal current is bound by the maximum current handling of the switches, maximum power dissipation of the package, and maximum applied voltage across any two of the A, B, and W terminals at a given resistance.

<sup>2</sup> Package power dissipation =  $(T_{JMAX} - T_A)/\theta_{JA}$ .

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

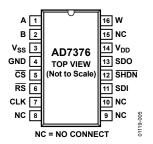

## **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

Figure 4. 14-Lead TSSOP Pin Configuration

Figure 5. 16-Lead SOIC\_W Pin Configuration

### **Table 6.Pin Function Descriptions**

| Pin No. |          |                 |                                                                                                              |

|---------|----------|-----------------|--------------------------------------------------------------------------------------------------------------|

| 14-Lead | 16-Lead  |                 |                                                                                                              |

| TSSOP   | SOL      | Mnemonic        | Description                                                                                                  |

| 1       | 1        | А               | A Terminal. $V_{SS} \leq V_A \leq V_{DD}$ .                                                                  |

| 2       | 2        | В               | B Terminal. $V_{SS} \leq V_B \leq V_{DD}$ .                                                                  |

| 3       | 3        | Vss             | Negative Power Supply.                                                                                       |

| 4       | 4        | GND             | Digital Ground.                                                                                              |

| 5       | 5        | CS              | Chip Select Input, Active Low. When CS returns high, data is loaded into the wiper register.                 |

| 6       | 6        | RS              | Reset to Midscale.                                                                                           |

| 7       | 7        | CLK             | Serial Clock Input. Positive edge triggered.                                                                 |

| 8       | 8, 9, 10 | NC              | No Connect. Let it float or ground.                                                                          |

| 9       | 11       | SDI             | Serial Data Input (data loads MSB first).                                                                    |

| 10      | 12       | SHDN            | Shutdown. A terminal open ended; W and B terminals shorted. Can be used as programmable preset. <sup>1</sup> |

| 11      | 13       | SDO             | Serial Data Output.                                                                                          |

| 12      | 14       | V <sub>DD</sub> | Positive Power Supply.                                                                                       |

| 13      | 15       | NC              | No Connect. Let it float or ground.                                                                          |

| 14      | 16       | W               | Wiper Terminal. $V_{SS} \le V_W \le V_{DD}$ .                                                                |

<sup>1</sup> Assert shutdown and program the device during power-up. Then, deassert the shutdown to achieve the desirable preset level.

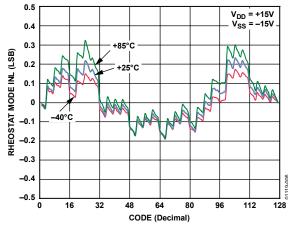

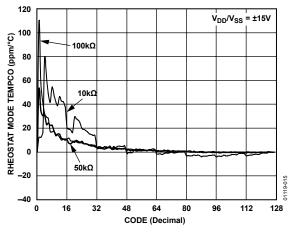

## **TYPICAL PERFORMANCE CHARACTERISTICS**

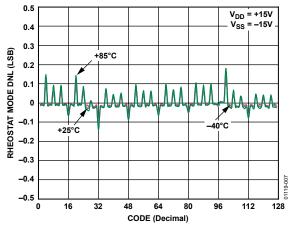

Figure 6. Resistance Step Position Nonlinearity Error vs. Code

Figure 7. Relative Resistance Step Change from Ideal vs. Code

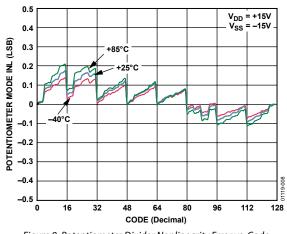

Figure 8. Potentiometer Divider Nonlinearity Error vs. Code

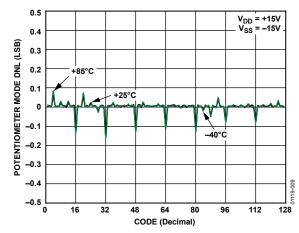

Figure 9. Potentiometer Divider Differential Nonlinearity Error vs. Code

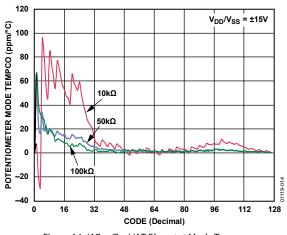

Figure 15. (ΔV<sub>WB</sub>/V<sub>WB</sub>)/ΔT Potentiometer Mode Tempco

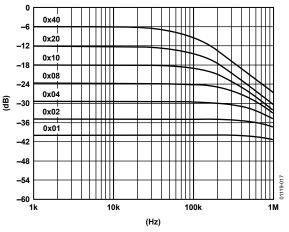

Figure 16. 10 k $\Omega$  Gain vs. Frequency vs. Code

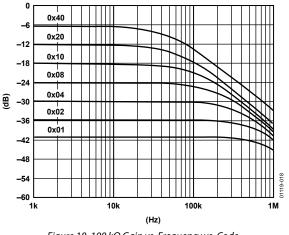

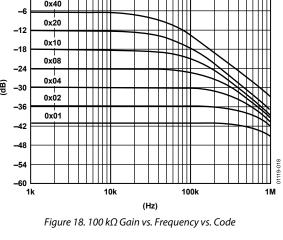

Figure 17. 50 k $\Omega$  Gain vs. Frequency vs. Code

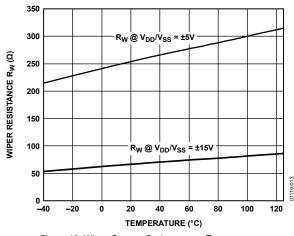

Figure 13. Wiper Contact Resistance vs. Temperature

Figure 14.  $(\Delta R_{WB}/R_{WB})/\Delta T$  Rheostat Mode Tempco

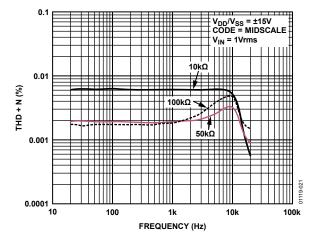

Figure 21. Total Harmonic Distortion Plus Noise vs. Frequency

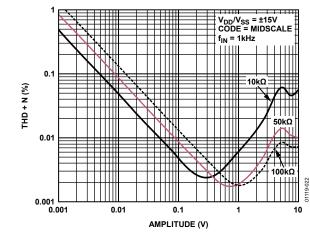

Figure 22. Total Harmonic Distortion Plus Noise vs. Amplitude

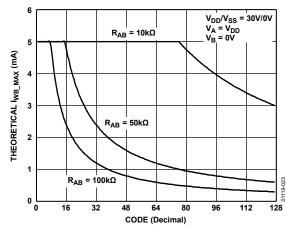

Figure 23. Theoretical Maximum Current vs. Code

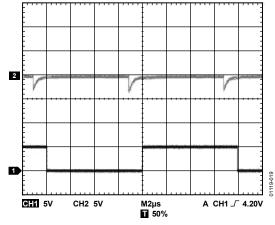

Figure 19. Midscale to Midscale – 1 Transition Glitch

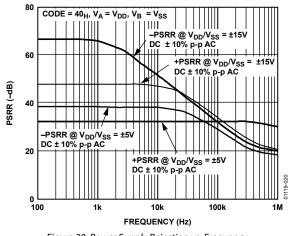

Figure 20. Power Supply Rejection vs. Frequency

## THEORY OF OPERATION PROGRAMMING THE VARIABLE RESISTOR

### **Rheostat Operation**

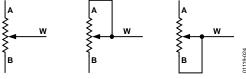

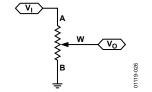

The part operates in rheostat mode when only two terminals are used as a variable resistor. The unused terminal can be left floating or tied to the W terminal as shown in Figure 24.

Figure 24. Rheostat Mode Configuration

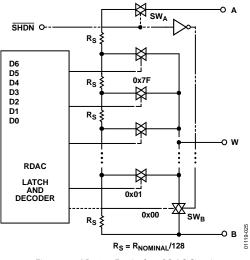

The nominal resistance between Terminals A and B,  $R_{AB}$ , is available in 10 k $\Omega$ , 50 k $\Omega$ , and 100 k $\Omega$  with ±30% tolerance and has 128 tap points accessed by the wiper terminal. The 7-bit data in the RDAC latch is decoded to select one of the 128 possible settings. Figure 25 shows a simplified RDAC structure.

Figure 25. AD7376 Equivalent RDAC Circuit

The general equation determining the digitally programmed output resistance between the W and the B terminals is

$$R_{WB}(D) = \frac{D}{128} \times R_{AB} + R_W \tag{1}$$

where:

*D* is the decimal equivalent of the binary code loaded in the 7-bit RDAC register from 0 to 127.

$R_{AB}$  is the end-to-end resistance.

$R_W$  is the wiper resistance contributed by the on resistance of the internal switch.

The AD7376 wiper switches are designed with the transmission gate CMOS topology, and the gate voltage is derived from the  $V_{\rm DD}$ . Each switch's on resistance,  $R_{\rm W}$ , is a function of  $V_{\rm DD}$  and temperature (see Figure 13).

Contrary to the temperature coefficient of  $R_{AB}$ , the temperature coefficient of the wiper resistance is significantly higher because the wiper resistance doubles with every 100° increase. As a result, the user must take into consideration the contribution of  $R_W$  on the desirable resistance. On the other hand, each switch's on resistance is insensitive to the tap point potential and remains relatively flat at 120  $\Omega$  typical at a  $V_{DD}$  of 15 V and a temperature of 25°C.

Assuming that a 10 k $\Omega$  part is used, the wiper's first connection starts at the B terminal for programming code 0x00, where SW<sub>B</sub> is closed. The minimum resistance between Terminals W and B is therefore 120  $\Omega$  in general. The second connection is the first tap point, which corresponds to 198  $\Omega$  ( $R_{WB} = 1/128 \times R_{AB} + R_W$ = 78  $\Omega$  + 120  $\Omega$ ) for programming code 0x01, and so on.

Each LSB data value increase moves the wiper up the resistor ladder until the last tap point is reached at 10,042  $\Omega$  ( $R_{AB}$  – 1 LSB +  $R_W$ ). Regardless of which settings the part is operating with, care should be taken to limit the current conducted between any A and B, W and A, or W and B terminals to a maximum dc current of 5 mA and a maximum pulse current of 20 mA. Otherwise, degradation or possible destruction of the internal switch contact can occur.

Similar to the mechanical potentiometer, the resistance of the RDAC between the W and A terminals also produces a digitally controlled complementary resistance,  $R_{WA}$ .

When these terminals are used, the B terminal can be opened. Setting the resistance value for  $R_{WA}$  starts at a maximum value of resistance and decreases as the data loaded into the latch increases in value. The general equation for this operation is

$$R_{WA}(D) = \frac{128 - D}{128} \times R_{AB} + R_{W}$$

(2)

### **PROGRAMMING THE POTENTIOMETER DIVIDER**

### Voltage Output Operation

The digital potentiometer easily generates a voltage divider at Wiper W to Terminal B and Wiper W to Terminal A that is proportional to the input voltage at Terminal A to Terminal B. Unlike the polarity of  $V_{\rm DD}$  to GND, which must be positive, voltage across Terminal A to Terminal B, Wiper W to Terminal A, and Wiper W to Terminal B can be at either polarity.

Figure 26. Potentiometer Mode Configuration

If ignoring the effect of the wiper resistance for the purpose of approximation, connecting the Terminal A to 30 V and the Terminal B to ground produces an output voltage at the Wiper W to Terminal B ranging from 0 V to 1 LSB less than 30 V. Each LSB of voltage is equal to the voltage applied across Terminals A and B divided by the 128 positions of the potentiometer divider. The general equation defining the output voltage at V<sub>w</sub> with respect to ground for any valid input voltage applied to Terminals A and B is

$$V_W(D) = \frac{D}{128} V_A \tag{3}$$

A more accurate calculation that includes the effect of wiper resistance,  $V_{W}$ , is

$$V_{W}(D) = \frac{R_{WB}(D)}{R_{AB}} V_{A} + \frac{R_{WA}(D)}{R_{AB}} V_{B}$$

(4)

Operation of the digital potentiometer in the divider mode results in a more accurate operation over temperature. Unlike when in rheostat mode, the output voltage in divider mode is primarily dependent on the ratio, not the absolute values, of the internal resistors  $R_{WA}$  and  $R_{WB}$ . Therefore, the temperature drift reduces to 5 ppm/°C.

### **3-WIRE SERIAL BUS DIGITAL INTERFACE**

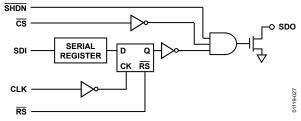

The AD7376 contains a 3-wire digital interface ( $\overline{CS}$ , CLK, and SDI). The 7-bit serial word must be loaded MSB first. The format of the word is shown in Figure 2. The positive edge-sensitive CLK input requires clean transitions to avoid clocking incorrect data into the serial input register. Standard logic families work well. When  $\overline{CS}$  is low, the clock loads data into the serial register upon each positive clock edge.

The data setup and hold times in Table 3 determine the valid timing requirements. The AD7376 uses a 7-bit serial input data register word that is transferred to the internal RDAC register when the  $\overline{\text{CS}}$  line returns to logic high. Extra MSB bits are ignored.

The AD7376 powers up at a random setting. However, the midscale preset or any desirable preset can be achieved by manipulating  $\overline{\text{RS}}$  or  $\overline{\text{SHDN}}$  with an extra I/O.

When the reset  $(\overline{\text{RS}})$  pin is asserted, the wiper resets to the midscale value. Midscale reset can be achieved dynamically or during power-up if an extra I/O is used.

When the  $\overline{\rm SHDN}$  pin is asserted, the AD7376 opens SW<sub>A</sub> to let the Terminal A float and to short Wiper W to Terminal B. The AD7376 consumes negligible power during the shutdown mode and resumes the previous setting once the  $\overline{\rm SHDN}$  pin is released. On the other hand, the AD7376 can be programmed with any settings during shutdown. With an extra programmable I/O asserting shutdown during power-up, this unique feature allows the AD7376 with programmable preset at any desirable level.

Table 7 shows the logic truth table for all operations.

Table 7. Input Logic Control Truth Table<sup>1</sup>

| CLK | CS | RS | SHDN | Register Activity                                                                                             |  |  |  |

|-----|----|----|------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| L   | L  | Н  | Н    | Enables SR, enables SDO pin.                                                                                  |  |  |  |

| Ρ   | L  | Н  | Н    | Shifts one bit in from the SDI pin. The seventh previously entered bit is shifted out of the SDO pin.         |  |  |  |

| Х   | Р  | н  | Н    | Loads SR data into 7-bit RDAC latch.                                                                          |  |  |  |

| Х   | Н  | н  | Н    | No operation.                                                                                                 |  |  |  |

| Х   | х  | L  | Н    | Sets 7-bit RDAC latch to midscale, wiper centered, and SDO latch cleared.                                     |  |  |  |

| Х   | Н  | Р  | Н    | Latches 7-bit RDAC latch to 0x40.                                                                             |  |  |  |

| Х   | Н  | Н  | L    | Opens circuits resistor of Terminal A,<br>connects Wiper W to Terminal B,<br>turns off SDO output transistor. |  |  |  |

$^{1}$  P = positive edge, X = don't care, and SR = shift register.

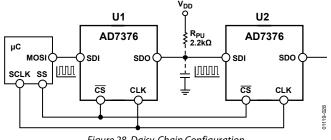

### **DAISY-CHAIN OPERATION**

Figure 27. Detailed SDO Output Schematic of the AD7376

Figure 27 shows the details of the serial data output pin (SDO). SDO shifts out the SDI content in the previous frame; therefore, it can be used for daisy-chaining multiple devices. The SDO pin contains an open-drain N-Channel MOSFET and requires a pull-up resistor if the SDO function is used.

Users need to tie the SDO pin of one package to the SDI pin of the next package. For example, in Figure 28, if two AD7376s are daisy-chained, a total of 14 bits of data are required for each operation. The first set of seven bits goes to U2; the second set of seven bits goes to U1. CS should be kept low until all 14 bits are clocked into their respective serial registers. Then CS is pulled high to complete the operation.

When daisy-chaining multiple devices, users may need to increase the clock period because the pull-up resistor and the capacitive loading at the SDO to SDI interface may induce a time delay to subsequent devices.

Figure 28. Daisy-Chain Configuration

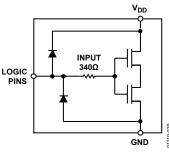

### **ESD PROTECTION**

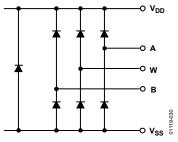

All digital inputs are protected with a series input resistor and an ESD structure shown in Figure 29. These structures apply to digital input pins CS, CLK, SDI, RS, and SHDN.

Figure 29. Equivalent ESD Protection Circuit

All analog terminals are also protected by ESD protection diodes, as shown in Figure 30.

Figure 30. Equivalent ESD Protection Analog Pins

### **TERMINAL VOLTAGE OPERATING RANGE**

The AD7376  $V_{DD}$  and  $V_{SS}$  power supplies define the boundary conditions for proper 3-terminal digital potentiometer operation. Applied signals present on Terminals A, B, and W that are more positive than  $V_{DD}$  or more negative than  $V_{SS}$  will be clamped by the internal forward-biased diodes (see Figure 30).

### **POWER-UP AND POWER-DOWN SEQUENCES**

Because of the ESD protection diodes that limit the voltage compliance at Terminals A, B, and W (see Figure 30), it is important to power V<sub>DD</sub>/V<sub>SS</sub> before applying voltage to Terminals A, B, and W. Otherwise, the diodes are forward biased such that VDD/VSS are powered unintentionally and affect the system. Similarly,  $V_{DD}/V_{SS}$  should be powered down last. The ideal power-up sequence is in the following order: GND,  $V_{DD}$ ,  $V_{SS}$ , digital inputs, and  $V_A/V_B/V_W$ . The order of powering V<sub>A</sub>, V<sub>B</sub>, V<sub>W</sub>, and the digital inputs is not important, as long as they are powered after VDD/VSS.

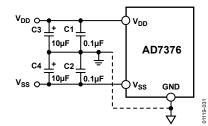

### LAYOUT AND POWER SUPPLY BIASING

It is a good practice to employ a compact, minimum lead-length layout design. The leads to the input should be as direct as possible, with a minimum conductor length. Ground paths should have low resistance and low inductance.

Similarly, it is also good practice to bypass the power supplies with quality capacitors. Low ESR (equivalent series resistance) 1  $\mu$ F to 10  $\mu$ F tantalum or electrolytic capacitors should be applied at the supplies to minimize transient disturbances and filter low frequency ripple. Figure 31 illustrates the basic supply bypassing configuration for the AD7376.

The ground pin of the AD7376 is a digital ground reference. To minimize the digital ground bounce, the AD7376 digital ground terminal should be joined remotely to the analog ground (see Figure 31).

Figure 31. Power Supply Bypassing

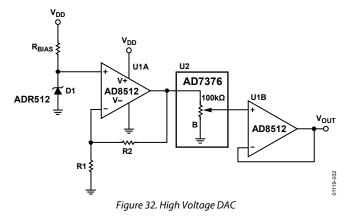

## APPLICATIONS INFORMATION high voltage dac

The AD7376 can be configured as a high voltage DAC as high as 30 V. The circuit is shown in Figure 32. The output is

$$V_{\rm O}(D) = \frac{D}{128} \left[ 1.2 \text{ V} \times \left( 1 + \frac{R^2}{R^1} \right) \right]$$

(5)

Where *D* is the decimal code from 0 to 127.

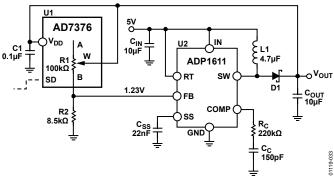

### **PROGRAMMABLE POWER SUPPLY**

With a boost regulator such as ADP1611, AD7376 can be used as the variable resistor at the regulator's FB pin to provide the programmable power supply (see Figure 33). The output is

$$V_{O} = 1.23 \text{ V} \times \left[ 1 + \frac{\left(\frac{D}{128}\right) \times R_{AB}}{R2} \right]$$

(6)

Note that the AD7376's  $V_{\rm DD}$  is derived from the output. Initially L1 acts as a short, and  $V_{\rm DD}$  is one diode voltage drop below +5 V. The output slowly establishes to the final value.

The AD7376 shutdown sleep-mode programming can be used to program a desirable preset level at power-up.

Figure 33. Programmable Power Supply

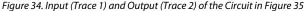

### **AUDIO VOLUME CONTROL**

Because of its good THD performance and high voltage capability, the AD7376 can be used for digital volume control. If AD7376 is used directly as an audio attenuator or gain amplifier, a large step change in the volume level at any arbitrary time can lead to an abrupt discontinuity of the audio signal, causing an audible zipper noise. To prevent this, a zero-crossing window detector can be inserted to the  $\overline{CS}$  line to delay the device update until the audio signal crosses the window. Since the input signal can operate on top of any dc levels rather than absolute zero volt level, zero-crossing, in this case, means the signal is ac-coupled and the dc offset level is the signal zero reference point.

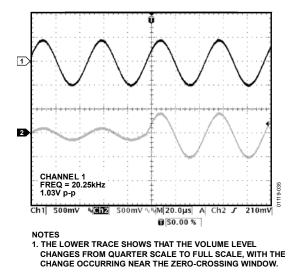

The configuration to reduce zipper noise and the result of using this configuration are shown in Figure 35 and Figure 34, respectively. The input is ac-coupled by C1 and attenuated down before feeding into the window comparator formed by U2, U3, and U4B. U6 is used to establish the signal zero reference. The upper limit of the comparator is set above its offset and, therefore, the output pulses high whenever the input falls between 2.502 V and 2.497 V (or 0.005 V window) in this example. This output is AND'ed with the chip select signal such that the AD7376 updates whenever the signal crosses the window. To avoid constant update of the device, the chip select signal should be programmed as two pulses, rather than the one shown in Figure 2.

In Figure 34, the lower trace shows that the volume level changes from a quarter scale to full scale when a signal change occurs near the zero-crossing window.

The AD7376 shutdown sleep-mode programming feature can be used to mute the device at power-up by holding  $\overline{\text{SHDN}}$  low and programming zero scale.

Figure 35. Audio Volume Control with Zipper Noise Reduction

## **OUTLINE DIMENSIONS**

Dimensions shown in millimeters and (inches)

030707-B

### **ORDERING GUIDE**

| Model                        | kΩ  | Temperature Range | Package Description <sup>1, 2</sup> | Package Option | Ordering Quantity |

|------------------------------|-----|-------------------|-------------------------------------|----------------|-------------------|

| AD7376AR10                   | 10  | -40°C to +85°C    | 16-Lead SOIC_W                      | RW-16          | 47                |

| AD7376AR10-REEL              | 10  | -40°C to +85°C    | 16-Lead SOIC_W                      | RW-16          | 1,000             |

| AD7376ARU10                  | 10  | -40°C to +85°C    | 14-Lead TSSOP                       | RU-14          | 96                |

| AD7376ARU10-REEL7            | 10  | -40°C to +85°C    | 14-Lead TSSOP                       | RU-14          | 1,000             |

| AD7376ARUZ10 <sup>3</sup>    | 10  | -40°C to +85°C    | 14-Lead TSSOP                       | RU-14          | 96                |

| AD7376ARUZ10-R7 <sup>3</sup> | 10  | -40°C to +85°C    | 14-Lead TSSOP                       | RU-14          | 1,000             |

| AD7376ARWZ10 <sup>3</sup>    | 10  | -40°C to +85°C    | 16-Lead SOIC_W                      | RW-16          | 47                |

| AD7376ARWZ10-RL <sup>3</sup> | 10  | -40°C to +85°C    | 16-Lead SOIC_W                      | RW-16          | 1,000             |

| AD7376ARUZ50-REEL7           | 50  | -40°C to +85°C    | 14-Lead TSSOP                       | RU-14          | 1,000             |

| AD7376ARUZ50 <sup>3</sup>    | 50  | –40°C to +85°C    | 14-Lead TSSOP                       | RU-14          | 96                |

| AD7376ARWZ50 <sup>3</sup>    | 50  | -40°C to +85°C    | 16-Lead SOIC_W                      | RW-16          | 47                |

| AD7376ARUZ1003               | 100 | -40°C to +85°C    | 14-Lead TSSOP                       | RU-14          | 96                |

| AD7376ARUZ100-R73            | 100 | –40°C to +85°C    | 14-Lead TSSOP                       | RU-14          | 1,000             |

| AD7376ARWZ100 <sup>3</sup>   | 100 | -40°C to +85°C    | 16-Lead SOIC_W                      | RW-16          | 47                |

| AD7376EVAL                   | 10  |                   |                                     |                | 1                 |

<sup>1</sup> In SOICWB-16 package top marking: line 1 shows AD7376; line 2 shows the branding information, where A10 = 10 k $\Omega$ , A50 = 50 k $\Omega$ , and A100 = 100 k $\Omega$ ; line 3 shows a "#" top marking with the date code in YYWW; and line 4 shows the lot number. <sup>2</sup> In TSSOP-14 package top marking: line 1 shows 7376; line 2 shows the branding information, where A10 = 10 k $\Omega$ , A50 = 50 k $\Omega$ , and A100 = 100 k $\Omega$ ; line 3 shows a "#" top marking with the date code in YWW; back side shows the lot number. <sup>3</sup> Z = RoHS compliant part.

## NOTES

www.analog.com

©1997-2007 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D01119-0-3/07(B)

Rev. B | Page 20 of 20